Analyse WCET Hybride pour Systèmes Multi-Cœurs

trait de séparation

Temps de lecture : 8 minutes • Février 2026

Pourquoi l’Analyse WCET est Cruciale

Dans les systèmes temps réel critiques, le respect strict des contraintes temporelles est aussi essentiel que la conformité fonctionnelle : chaque tâche doit impérativement terminer son exécution avant sa date limite. Pour garantir cela, il est indispensable de disposer de bornes fiables du Worst-Case Execution Time (WCET), c’est‑à‑dire le temps maximal que pourrait prendre une tâche dans son pire scénario d’exécution.

Pendant longtemps, la pratique courante consistait à réaliser des mesures dites « end-to-end ». Bien que simples à mettre en œuvre, ces mesures ne reflètent qu’un seul scénario d’entrée et ne prennent pas en compte l’ensemble des états matériels possibles. Or, sur des architectures modernes comportant caches, pipelines, exécution spéculative ou ressources partagées, le temps d’exécution dépend fortement de l’historique d’exécution. Une couverture de test exhaustive est alors impossible, et ces mesures ne peuvent fournir aucune garantie sûre.

Face à ces limites, l’analyse statique par Interprétation Abstraite propose une alternative permettant de fournir des bornes sûres, indépendantes des scénarios d’entrée. Cependant, elle repose sur des modèles précis du processeur et du SoC (System-on-Chip). Sur des processeurs multicœurs modernes, souvent complexes, partiellement documentés ou intégrant des comportements non déterministes, ces modèles deviennent difficiles à établir conduisant à des résultats analytiques parfois trop pessimistes.

C’est précisément pour combler cet écart entre précision et sûreté qu’émerge l’analyse WCET hybride. Cette approche combine les forces des deux mondes :

L’analyse hybride permet ainsi d’observer des comportements matériels impossibles à modéliser entièrement, tout en s’appuyant sur une exploration systématique des chemins d’exécution. Elle fournit des estimations temporelles à la fois réalistes, sensibles aux interférences, et suffisamment sûres pour répondre aux exigences des normes de certification, notamment lorsque les architectures multicœurs ne permettent pas un partitionnement temporel robuste.

Pendant longtemps, la pratique courante consistait à réaliser des mesures dites « end-to-end ». Bien que simples à mettre en œuvre, ces mesures ne reflètent qu’un seul scénario d’entrée et ne prennent pas en compte l’ensemble des états matériels possibles. Or, sur des architectures modernes comportant caches, pipelines, exécution spéculative ou ressources partagées, le temps d’exécution dépend fortement de l’historique d’exécution. Une couverture de test exhaustive est alors impossible, et ces mesures ne peuvent fournir aucune garantie sûre.

Face à ces limites, l’analyse statique par Interprétation Abstraite propose une alternative permettant de fournir des bornes sûres, indépendantes des scénarios d’entrée. Cependant, elle repose sur des modèles précis du processeur et du SoC (System-on-Chip). Sur des processeurs multicœurs modernes, souvent complexes, partiellement documentés ou intégrant des comportements non déterministes, ces modèles deviennent difficiles à établir conduisant à des résultats analytiques parfois trop pessimistes.

C’est précisément pour combler cet écart entre précision et sûreté qu’émerge l’analyse WCET hybride. Cette approche combine les forces des deux mondes :

- Les garanties structurelles de l’analyse statique, qui reconstruit les chemins d’exécution possibles,

- Et les mesures non intrusives issues de l’exécution réelle, qui capturent les effets concrets des caches, bus, pipelines et interférences entre cœurs.

L’analyse hybride permet ainsi d’observer des comportements matériels impossibles à modéliser entièrement, tout en s’appuyant sur une exploration systématique des chemins d’exécution. Elle fournit des estimations temporelles à la fois réalistes, sensibles aux interférences, et suffisamment sûres pour répondre aux exigences des normes de certification, notamment lorsque les architectures multicœurs ne permettent pas un partitionnement temporel robuste.

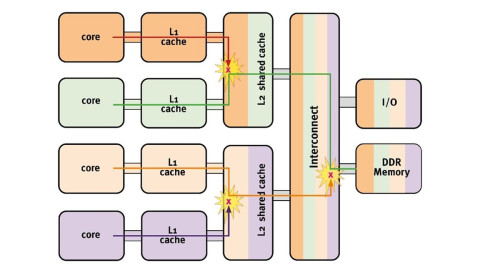

Le défi : Interférences et Imprévisibilité des Processeurs Multicœurs

L’introduction des processeurs multicœurs (MCP) dans les systèmes embarqués critiques a profondément modifié les problématiques liées à l’analyse temporelle. Bien qu’ils offrent davantage de puissance de calcul, ils introduisent une forte variabilité temporelle due au partage de ressources matérielles : mémoire externe, caches, bus, interconnexions, etc. Lorsque plusieurs cœurs sollicitent simultanément ces ressources, des interférences inter‑cœurs apparaissent, provoquant des fluctuations parfois importantes des latences, notamment lors des accès mémoire.

C’est précisément cette source d’imprévisibilité que met en avant l’EASA AMC 20‑193. Le document souligne que ces interférences peuvent rendre le comportement d’applications critiques non déterministe, compromettant leur capacité à respecter leurs contraintes temporelles. AMC 20‑193 impose donc d’évaluer rigoureusement l’impact des interférences et d’apporter des garanties démontrables, particulièrement pour les systèmes soumis à des niveaux d’assurance élevés (DAL A, B ou C). Lorsque le processeur ne fournit pas un partitionnement robuste du temps et des ressources, l’évaluation doit impérativement être menée dans la configuration opérationnelle réelle, avec l’ensemble des logiciels actifs.

Dans ce contexte, les approches traditionnelles qu’il s’agisse de mesures « end-to-end » ou analyse statique isolée se révèlent insuffisantes pour appréhender correctement les effets de contention propres aux architectures multicœurs. Leur incapacité à capturer la variabilité réelle, ou au contraire leur tendance à produire des bornes excessivement conservatrices, démontre la nécessité d’une méthode adaptée aux contraintes modernes. C’est précisément dans ce cadre que s’inscrit l’analyse WCET hybride, qui constitue le socle méthodologique permettant d’aborder les interférences multicœurs de manière systématique et conforme aux exigences de l’AMC 20‑193.

C’est précisément cette source d’imprévisibilité que met en avant l’EASA AMC 20‑193. Le document souligne que ces interférences peuvent rendre le comportement d’applications critiques non déterministe, compromettant leur capacité à respecter leurs contraintes temporelles. AMC 20‑193 impose donc d’évaluer rigoureusement l’impact des interférences et d’apporter des garanties démontrables, particulièrement pour les systèmes soumis à des niveaux d’assurance élevés (DAL A, B ou C). Lorsque le processeur ne fournit pas un partitionnement robuste du temps et des ressources, l’évaluation doit impérativement être menée dans la configuration opérationnelle réelle, avec l’ensemble des logiciels actifs.

Dans ce contexte, les approches traditionnelles qu’il s’agisse de mesures « end-to-end » ou analyse statique isolée se révèlent insuffisantes pour appréhender correctement les effets de contention propres aux architectures multicœurs. Leur incapacité à capturer la variabilité réelle, ou au contraire leur tendance à produire des bornes excessivement conservatrices, démontre la nécessité d’une méthode adaptée aux contraintes modernes. C’est précisément dans ce cadre que s’inscrit l’analyse WCET hybride, qui constitue le socle méthodologique permettant d’aborder les interférences multicœurs de manière systématique et conforme aux exigences de l’AMC 20‑193.

TimeWeaver : une Analyse WCET Hybride Structurée

TimeWeaver met en œuvre l’analyse hybride selon un processus en quatre étapes principales :

Les traces sont associées aux blocs du CFG et fournissent des temps d’exécution précis tenant compte des interférences réelles. L’extrapolation IPET combine ces segments pour identifier un chemin pire‑cas, même si celui‑ci n’a jamais été observé en une seule fois. L’exploitation des traces ETU telles qu’ARM CoreSight™, Infineon MCDS™, Nexus IEEE-ISTO5001™ présentes sur les architectures ARM, PowerPC, RH850, TriCore/AURIX permet d’éviter « l’effet de sonde » des approches instrumentées

TimeWeaver fournit également des métriques essentielles :

Limite pratique des ETU standard : l’analyse hybride de TimeWeaver repose sur des traces issues des ETU. Toutefois, la bande passante limitée et la capacité restreinte des buffers de certaines solutions de Trace réduisent fortement la durée d’observation possible. Quelques secondes ou minutes suffisent souvent à saturer la mémoire de trace, diminuant ainsi la probabilité de capturer des événements rares ou des pires cas dépendant de séquences longues.

1. Décodage et reconstruction du graphe de flot de contrôle (CFG) à partir du binaire.

2. Analyse des boucles, valeurs et chemins, avec élimination des chemins infaisables.

3. Analyse de traces non intrusives issues des unités de trace embarquées (ETU).

4. Extrapolation du pire chemin via un modèle linéaire entier (IPET).

Les traces sont associées aux blocs du CFG et fournissent des temps d’exécution précis tenant compte des interférences réelles. L’extrapolation IPET combine ces segments pour identifier un chemin pire‑cas, même si celui‑ci n’a jamais été observé en une seule fois. L’exploitation des traces ETU telles qu’ARM CoreSight™, Infineon MCDS™, Nexus IEEE-ISTO5001™ présentes sur les architectures ARM, PowerPC, RH850, TriCore/AURIX permet d’éviter « l’effet de sonde » des approches instrumentées

TimeWeaver fournit également des métriques essentielles :

- Couverture des blocs, instructions et transitions,

- Couverture des flows (prédécesseur → bloc → successeur),

- Statistiques temporelles détaillées (min, max, moyenne, écart‑type),

- Identification des boucles insuffisamment couvertes.

Limite pratique des ETU standard : l’analyse hybride de TimeWeaver repose sur des traces issues des ETU. Toutefois, la bande passante limitée et la capacité restreinte des buffers de certaines solutions de Trace réduisent fortement la durée d’observation possible. Quelques secondes ou minutes suffisent souvent à saturer la mémoire de trace, diminuant ainsi la probabilité de capturer des événements rares ou des pires cas dépendant de séquences longues.

CEDARtools : Observation Continue et Sélection Intelligente des Traces

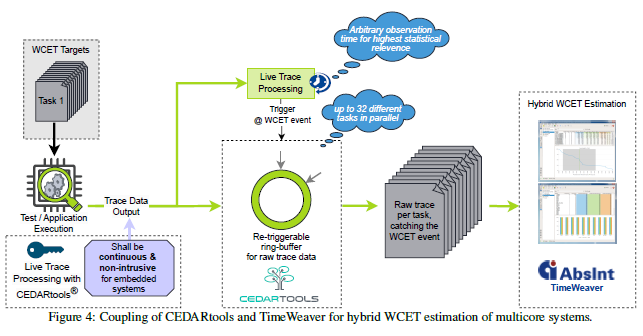

Pour lever ces limitations un dispositif capable de traiter les traces en continu, de filtrer automatiquement les séquences pertinentes et d’étendre la durée d’observation est nécessaire : c’est tout l’apport de la solution CEDARtools.

CEDARtools exploite le flux de traceen temps réel grâce à un traitement matériel (FPGA) capable de reconstruire le flot d’exécution à haute vitesse. Plutôt que de stocker l’intégralité des traces, ce qui serait impossible sur la durée, il conserve uniquement les séquences pertinentes grâce à des déclencheurs intelligents : dépassement d’un temps d’exécution, événement rare, comportement anormal, etc.

CEDARtools exploite le flux de traceen temps réel grâce à un traitement matériel (FPGA) capable de reconstruire le flot d’exécution à haute vitesse. Plutôt que de stocker l’intégralité des traces, ce qui serait impossible sur la durée, il conserve uniquement les séquences pertinentes grâce à des déclencheurs intelligents : dépassement d’un temps d’exécution, événement rare, comportement anormal, etc.

Couplage TimeWeaver × CEDARtools : Une Approche Complète et Conforme AMC 20‑193

Le couplage des deux outils suit un déroulement optimal :

1. Le système cible exécute l’application réelle dans sa configuration rfinale.

2. CEDARtools reconstruit le flot et conserve les traces pertinentes.

3. Les traces sélectionnées sont analysées par TimeWeaver.

4. L’analyse IPET reconstitue le pire chemin possible.

5. Les rapports de couverture orientent de nouvelles captures si nécessaire.

Cette combinaison permet d’intégrer directement les effets d’interférences multicœurs, tout en garantissant une estimation sûre et traçable et conforme aux attentes AMC 20‑193.

1. Le système cible exécute l’application réelle dans sa configuration rfinale.

2. CEDARtools reconstruit le flot et conserve les traces pertinentes.

3. Les traces sélectionnées sont analysées par TimeWeaver.

4. L’analyse IPET reconstitue le pire chemin possible.

5. Les rapports de couverture orientent de nouvelles captures si nécessaire.

Cette combinaison permet d’intégrer directement les effets d’interférences multicœurs, tout en garantissant une estimation sûre et traçable et conforme aux attentes AMC 20‑193.

Conclusion

L’analyse WCET hybride constitue aujourd’hui la méthode la plus réaliste et la plus robuste pour releverles défis posés par les architectures multicœurs dans les systèmes temps réel critiques.

Elle dépasse les limitations des approches traditionnelles et apporte une vision fidèle du comportement temporel. Le couplage TimeWeaver × CEDARtools offre un cadre complet, opérationnel et conforme aux exigences réglementaires. Cette approche permet non seulement d’identifier les scénarios extrêmes, mais aussi de fournir les preuves demandées par l’EASA AMC 20‑193.

En adoptant ces outils et cette méthodologie, les industriels disposent d’un fiable pour maîtriser les comportements temporels complexes des processeurs multicœurs, et développer des systèmes embarqués performants, sûrs et certifiables.

L’analyse WCET hybride constitue aujourd’hui la méthode la plus réaliste et la plus robuste pour releverles défis posés par les architectures multicœurs dans les systèmes temps réel critiques.

Elle dépasse les limitations des approches traditionnelles et apporte une vision fidèle du comportement temporel. Le couplage TimeWeaver × CEDARtools offre un cadre complet, opérationnel et conforme aux exigences réglementaires. Cette approche permet non seulement d’identifier les scénarios extrêmes, mais aussi de fournir les preuves demandées par l’EASA AMC 20‑193.

En adoptant ces outils et cette méthodologie, les industriels disposent d’un fiable pour maîtriser les comportements temporels complexes des processeurs multicœurs, et développer des systèmes embarqués performants, sûrs et certifiables.