XJFlash : Programmez In Situ des mémoires flash via JTAG

XJFlash, une méthode avancée et innovante de programmation In Situ de composants Flash via JTAG !

XJTAG permet de programmer des composants tels que des CPLD et des mémoires Flash en utilisant des fichiers SVF ou STAPL standard ou en utilisant des scripts écrits dans le langage de haut niveau de XJTAG, XJEase. Les ingénieurs peuvent également utiliser la solution XJFlash d’XJTAG pour programmer les mémoires Flash beaucoup plus rapidement qu’en gérant les données de manière conventionnelle dans la chaîne Boundary Scan de la carte.

En effet, la vitesse de programmation peut encore être améliorée avec XJFlash, qui peut programmer une Flash à une vitesse proche de sa vitesse maximale théorique.

XJTAG permet de programmer des composants tels que des CPLD et des mémoires Flash en utilisant des fichiers SVF ou STAPL standard ou en utilisant des scripts écrits dans le langage de haut niveau de XJTAG, XJEase. Les ingénieurs peuvent également utiliser la solution XJFlash d’XJTAG pour programmer les mémoires Flash beaucoup plus rapidement qu’en gérant les données de manière conventionnelle dans la chaîne Boundary Scan de la carte.

En effet, la vitesse de programmation peut encore être améliorée avec XJFlash, qui peut programmer une Flash à une vitesse proche de sa vitesse maximale théorique.

Comment fonctionne XJFlash ?

XJFlash vous permet de générer automatiquement des solutions de programmation personnalisées pour les composants Flash connectés aux FPGAs sur votre carte.

Les capacités fonctionnelles du FPGA sont exploitées pour obtenir des vitesses de programmation les plus rapides possibles. XJFlash génère automatiquement un design personnalisé pour chaque combinaison FPGA / flash, vous permettant de bénéficier des meilleurs temps de programmation, sans que vous ayez à effectuer de développement FPGA. Que vous utilisiez une flash SPI, QSPI ou parallèle NOR connectée à un FPGA d'Altera, Xilinx, Microsemi ou Lattice, XJFlash vous fournira une solution de programmation optimisée pour votre carte.

XJFlash crée une image FPGA, qui produit des cycles de lecture et d'écriture, le FPGA agissant alors comme un programmateur flash. Cette méthode utilise la capacité de transfert de données complète des broches JTAG.

Les capacités fonctionnelles du FPGA sont exploitées pour obtenir des vitesses de programmation les plus rapides possibles. XJFlash génère automatiquement un design personnalisé pour chaque combinaison FPGA / flash, vous permettant de bénéficier des meilleurs temps de programmation, sans que vous ayez à effectuer de développement FPGA. Que vous utilisiez une flash SPI, QSPI ou parallèle NOR connectée à un FPGA d'Altera, Xilinx, Microsemi ou Lattice, XJFlash vous fournira une solution de programmation optimisée pour votre carte.

XJFlash crée une image FPGA, qui produit des cycles de lecture et d'écriture, le FPGA agissant alors comme un programmateur flash. Cette méthode utilise la capacité de transfert de données complète des broches JTAG.

Temps de programmation avec XJFlash :

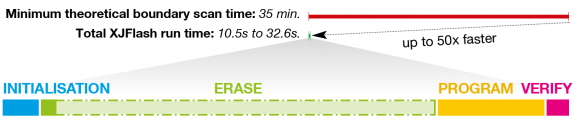

Dans la figure ci-dessous, nous montrons un exemple réel de la programmation accélérée avec XJFlash, qui est capable d'aller 50 fois plus vite que ce qui serait considéré comme normal en utilisant JTAG conventionnellement. Avec XJFlash, c’est d’ailleurs souvent le temps de programmation intrinsèque de la flash qui devient la limite de vitesse pour le process global de programmation.

Il s’agit d’un exemple typique, et la vitesse ici a été limitée par la puce flash et non par le système de programmation.

- Initialisation : Le FPGA connecté à la flash est configuré avec l'image XJFlash requise pour la carte cible. Pour l’exemple ci-dessus : temps de 2.1 s.

- Erase : La flash peut être effacée en utilisant l'un des deux algorithmes. L'effacement de base efface simplement tous les blocs dans une plage définie. L'effacement plus intelligent utilisera le fait qu'il est plus rapide de lire la flash que de l'effacer ; en tant que tel, il lit à partir de chaque adresse et ne commence à effacer que si certaines données sont trouvées. Cette étape peut être ignorée si l'on sait que la flash sera toujours vide avant sa programmation. Exemple de durée ci-dessus : effacement intelligent activé de 0,9 s avec un composant déjà effacé, à 23 s avec un composant entièrement programmé.

- Program : Les données provenant des images cibles sont diffusées dans le FPGA via son port JTAG. Le FPGA programme ensuite ces données dans la ou les flashs connectées. Plusieurs fichiers peuvent être spécifiés et programmés à des décalages définis.

Exemple de temps ci-dessus : 6,2 s (limité par la vitesse de programmation du composant) - Verify : La vérification vérifie chaque octet dans le flash par rapport au(x) fichier(s) spécifié(s), en veillant à ce qu'il n'y ait pas d'erreur de bit de données.

Exemple de temps ci-dessus : 1,8 s avec TCK à 10 MHz, réduit à 1,3 s avec TCK à 20 MHz.

Quand XJFlash peut-il être utilisé ?

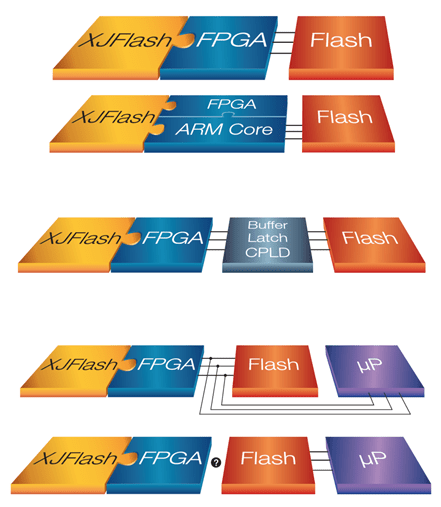

Pour pouvoir utiliser XJFlash, tous les signaux de données, d'adresse et de contrôle du ou des composants flash doivent être connectés à un FPGA sur la carte cible. Ces connexions peuvent être directes, indirectes, dédiées ou partagées :

Connexion directe

Fonctionne aussi avec un Soc

Fonctionne si :

- Flash connectée via un buffer

- Les signaux d'adresse sont verrouillés

- Il existe un autre composant configurable entre FPGA et la flash

Connexions partagées avec un autre composant

Aucune connexion - oui, avec des modifications de conception

Un seul outil pour tester et programmer :

De nombreux composants programmables modernes, tels que les FPGA et CPLD, sont conçus non seulement pour être compatible JTAG facilitant ainsi les tests (en phase prototypage et/ou production), mais aussi avec des fonctionnalités JTAG supplémentaires pour leur permettre d’être programmés après avoir été implémentés sur un circuit imprimé.

Avec XJFlash, les mémoires flash peuvent être programmées indirectement à travers leur connexion à des FPGAs contrôlés directement par la chaîne JTAG. XJFlash s’appuyant sur le contrôleur XJTAG, utilisé pour accéder à la carte pour le test en phase prototype et/ou production, il est possible de programmer simplement la carte sans investissement supplémentaire.

La possibilité d’utiliser des composants JTAG pour la programmation in-situ évite d’avoir à acheter des programmeurs dédiés peu efficaces et coûteux. En plus, il est alors facile de faire les mises à jour des logiciels ou des données contenues dans le composant, pendant la mise au point en phase prototypage par exemple, ou en phase production pour des mises à niveau de l’équipement.

Avec XJFlash, les mémoires flash peuvent être programmées indirectement à travers leur connexion à des FPGAs contrôlés directement par la chaîne JTAG. XJFlash s’appuyant sur le contrôleur XJTAG, utilisé pour accéder à la carte pour le test en phase prototype et/ou production, il est possible de programmer simplement la carte sans investissement supplémentaire.

La possibilité d’utiliser des composants JTAG pour la programmation in-situ évite d’avoir à acheter des programmeurs dédiés peu efficaces et coûteux. En plus, il est alors facile de faire les mises à jour des logiciels ou des données contenues dans le composant, pendant la mise au point en phase prototypage par exemple, ou en phase production pour des mises à niveau de l’équipement.

Autres lectures susceptibles de vous intéresser :

- JTAG est bien plus que du débogage et de la programmation. Apprenez comment utiliser boundary scan pour tester les cartes : Qu'est-ce que JTAG - et comment en tirer parti ? : https://www.xjtag.com/wp-content/uploads/xjtag-ebook_what-is-jtag-fr.pdf

- Pour plus d’informations sur XJFlash : https://www.xjtag.com/products/software/xjflash/