Réduire le Coût de la Qualité grâce au Test JTAG

trait de séparation

Temps de lecture : 5 minutes • Mars 2026

Lorsqu’on développe ou industrialise une carte électronique, chaque défaut non détecté peut coûter très chèr. Dans l’article original de Peter Fryers (XJTAG), le Coût de la Qualité (COQ) est présenté comme un outil stratégique permettant de comprendre où vont réellement les budgets de tests, et comment optimiser l’effort pour éviter les retours produit et les rappels catastrophiques.

Cet article revisite ces concepts, en insistant sur les implications spécifiques pour les experts JTAG et les ingénieurs de test.

Qu’est‑ce que le « Coût de la Qualité » en électronique ?

Le COQ englobe toutes les dépenses liées à la conformité ou non‑conformité d’un produit électronique.

Il inclut :

L’objectif : détecter les problèmes au plus tôt, car un défaut trouvé en production coûte toujours plus cher qu’un défaut détecté au prototypage et encore plus s’il atteint le client.

Il inclut :

- Prévention : conception orientée test, review de schémas, simulations.

- Évaluation : tests fonctionnels, boundary scan, inspection visuelle ou optique.

- Défaillances internes : retouches, rebuts production.

- Défaillances externes : retours terrain, rappels produits, pénalités client.

L’objectif : détecter les problèmes au plus tôt, car un défaut trouvé en production coûte toujours plus cher qu’un défaut détecté au prototypage et encore plus s’il atteint le client.

Les défis uniques des Tests Électroniques

Contrairement à d’autres industries, un simple contrôle visuel ne suffit pas.

XJTAG rappelle trois défis majeurs :

1️⃣ Test Coverage – Tester toute la fonctionnalité

Même les cas peu probables doivent être validés (ex. appel d'urgence sur smartphone sans réseau).

2️⃣ Test Recall – Avoir confiance dans les résultats

Un test est utile uniquement si l’on peut affirmer que la défaillance provient du produit, pas du banc.

3️⃣ Test Repeatability – Détecter les défauts intermittents ou latents

Certains défauts ne se manifestent pas immédiatement : via fissurée, soudure fragile, tension marginale… autant de facteurs que les tests doivent capturer.

XJTAG rappelle trois défis majeurs :

1️⃣ Test Coverage – Tester toute la fonctionnalité

Même les cas peu probables doivent être validés (ex. appel d'urgence sur smartphone sans réseau).

2️⃣ Test Recall – Avoir confiance dans les résultats

Un test est utile uniquement si l’on peut affirmer que la défaillance provient du produit, pas du banc.

3️⃣ Test Repeatability – Détecter les défauts intermittents ou latents

Certains défauts ne se manifestent pas immédiatement : via fissurée, soudure fragile, tension marginale… autant de facteurs que les tests doivent capturer.

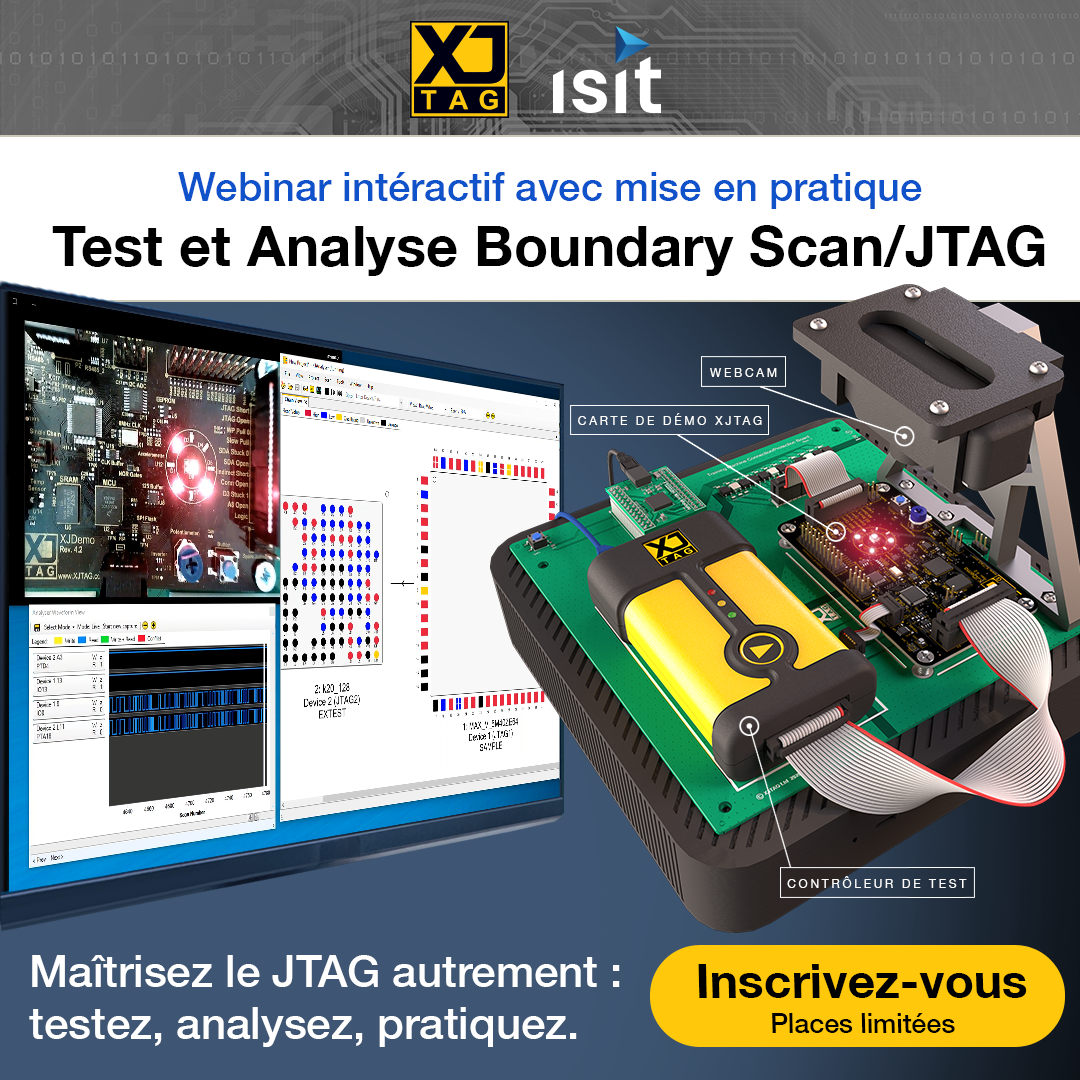

Pourquoi le JTAG / Boundary Scan est Essentiel pour Réduire le COQ

Le boundary scan (IEEE 1149.x) est un outil clé pour réduire les coûts de test :

En d'autres termes : plus de couverture avec moins de coûts, exactement ce que recherche tout responsable qualité.

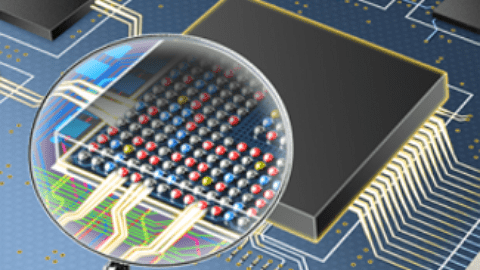

- Il augmente la testabilité sans nécessiter d’accès physique.

- Il permet de détecter tôt les courts‑circuits, ouvertures, composants manquants.

- Il couvre les zones inaccessibles (BGAs).

- Il s’intègre du prototype à la production sans redesign d’outillage.

En d'autres termes : plus de couverture avec moins de coûts, exactement ce que recherche tout responsable qualité.

Rework précoce et diagnostic

Le COQ met l’accent sur l’importance de corriger tôt : un défaut découvert au prototypage coûte 10× moins qu’en production, et 100× moins qu’en post‑production.

XJTAG insiste sur l’importance :

XJTAG insiste sur l’importance :

- d’un environnement de debug performant (ex. XJDeveloper, XJAnalyser),

- d’une méthodologie de test qui détecte aussi les défauts futurs (défaillances latentes).

Concevoir pour être testé : DFT + JTAG

Intégrer la testabilité dès la conception (Design for Test) est une des meilleures façons de réduire le COQ. Cela implique :

Plus tôt on construit une chaîne JTAG robuste, plus tôt on peut générer un Test Coverage Report et corriger les erreurs de design.

- Ajouter les points JTAG.

- Vérifier l’intégrité de la chaîne JTAG.

- S’assurer que les réseaux critiques sont accessibles via boundary scan.

Plus tôt on construit une chaîne JTAG robuste, plus tôt on peut générer un Test Coverage Report et corriger les erreurs de design.

Trouver l’équilibre : ni trop, ni trop peu

Un test “trop léger” laisse passer des défauts.

Un test “trop lourd” ralentit la production et fait exploser les budgets.

Le COQ permet de justifier auprès de la direction où se trouve le juste milieu.

C’est aussi un argument puissant pour investir dans un outil comme XJTAG, qui maximise la couverture tout en contrôlant les coûts.

Un test “trop lourd” ralentit la production et fait exploser les budgets.

Le COQ permet de justifier auprès de la direction où se trouve le juste milieu.

C’est aussi un argument puissant pour investir dans un outil comme XJTAG, qui maximise la couverture tout en contrôlant les coûts.

Conclusion : Le Boundary Scan, un Investissement COQ Intelligent

Le Cost of Quality (CoQ) n’est pas seulement une théorie : c’est une grille d’analyse indispensable pour les ingénieurs de test et les programmeurs JTAG.

Comprendre et optimiser test coverage, recall et repeatability permet de réduire les coûts, améliorer la fiabilité et accélérer la mise sur le marché.

Comprendre et optimiser test coverage, recall et repeatability permet de réduire les coûts, améliorer la fiabilité et accélérer la mise sur le marché.