Comprendre le JTAG

trait de séparation

Temps de lecture : 5 minutes • Septembre 2025

Une technologie méconnue aux multiples usages

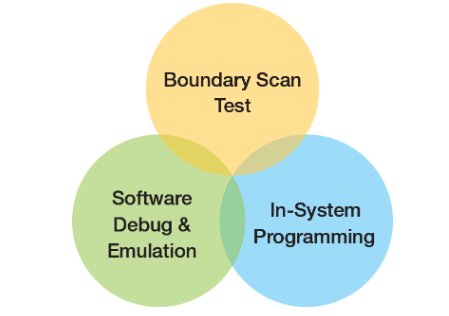

Vous avez peut-être déjà croisé le terme JTAG en utilisant des outils de programmation de processeurs, ou lors du débogage de systèmes embarqués. Il est vrai que la majorité des processeurs s’appuient sur JTAG pour activer les fonctions de débogage ou d’émulation, tout comme la quasi-totalité des FPGA et CPLD utilisent JTAG pour la programmation.

Mais réduire JTAG à ces seules fonctions serait passer à côté de tout son potentiel.

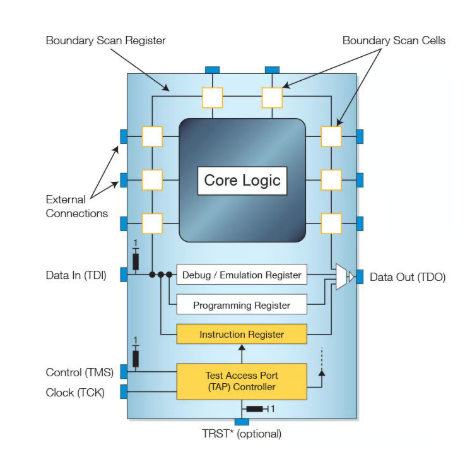

En réalité, ces cas d’usage ne mobilisent qu’une partie de la norme IEEE 1149.1, à savoir les quatre signaux du TAP (Test Access Port). Cette interface série a été conçue à l’origine pour permettre le test des circuits imprimés (PCB) sans devoir recourir à des sondes physiques complexes ou à des bancs de test sur mesure.

Mais réduire JTAG à ces seules fonctions serait passer à côté de tout son potentiel.

En réalité, ces cas d’usage ne mobilisent qu’une partie de la norme IEEE 1149.1, à savoir les quatre signaux du TAP (Test Access Port). Cette interface série a été conçue à l’origine pour permettre le test des circuits imprimés (PCB) sans devoir recourir à des sondes physiques complexes ou à des bancs de test sur mesure.

Le boundary scan : cœur du test via JTAG

Le composant central du test JTAG est le registre de scan de frontière (Boundary Scan Register, ou BSR). Il est placé à la frontière entre le cœur fonctionnel d’un composant et ses broches de connexion.

En mode de test, ce registre permet de piloter les signaux émis par un composant ou de surveiller l’état de ces signaux – tout cela sans interférer avec le fonctionnement normal du système.

Ce découplage facilite grandement la mise en place de tests, car il supprime le besoin de configurer ou de booter un composant pour accéder à ses broches. En somme, avec seulement quatre signaux (TCK, TMS, TDI, TDO), on peut observer et contrôler de manière fine une carte électronique.

En mode de test, ce registre permet de piloter les signaux émis par un composant ou de surveiller l’état de ces signaux – tout cela sans interférer avec le fonctionnement normal du système.

Ce découplage facilite grandement la mise en place de tests, car il supprime le besoin de configurer ou de booter un composant pour accéder à ses broches. En somme, avec seulement quatre signaux (TCK, TMS, TDI, TDO), on peut observer et contrôler de manière fine une carte électronique.

Comment XJTAG tire parti de JTAG pour tester vos cartes

XJTAG utilise le boundary scan selon deux approches complémentaires :

Par exemple, on peut allumer une LED et demander à un opérateur de confirmer sa mise sous tension, ou bien écrire/lire des données dans une mémoire RAM pour vérifier l’intégrité des lignes de communication.

- Le test de connexions : permet de vérifier les interconnexions entre composants JTAG. On détecte ainsi les courts-circuits, erreurs de soudure, résistances manquantes ou défauts de type stuck-at.

- Le test fonctionnel étendu : permet de tester des composants non-JTAG (mémoire DDR, Flash, capteurs SPI/I²C, etc.) en les pilotant via des composants JTAG.

Par exemple, on peut allumer une LED et demander à un opérateur de confirmer sa mise sous tension, ou bien écrire/lire des données dans une mémoire RAM pour vérifier l’intégrité des lignes de communication.

Qu’en est-il des composants non compatibles JTAG ?

Même si processeurs et FPGA sont souvent compatibles JTAG, une carte typique contient de nombreux composants qui ne le sont pas : DDR, SRAM, capteurs, EEPROM, ADC, DAC, etc.

XJTAG permet tout de même de tester les connexions reliant ces périphériques aux composants JTAG. Mais pour détecter les circuits ouverts, il faut aller plus loin et établir une communication active avec ces périphériques.

XJTAG permet tout de même de tester les connexions reliant ces périphériques aux composants JTAG. Mais pour détecter les circuits ouverts, il faut aller plus loin et établir une communication active avec ces périphériques.

Un système de test facile à mettre en place

Grâce à la bibliothèque de modèles XJTAG, qui couvre des composants simples (résistances, buffers) jusqu’aux mémoires complexes (DDR3…), vous pouvez lancer des tests sans écrire une seule ligne de code.

Aucune modification de design n’est nécessaire si un connecteur JTAG est déjà prévu – ce qui est le cas dans la majorité des cartes modernes.

Aucune modification de design n’est nécessaire si un connecteur JTAG est déjà prévu – ce qui est le cas dans la majorité des cartes modernes.

Les fichiers BSDL : indispensables pour tester

Pour tout test JTAG, il est nécessaire de disposer du fichier BSDL (Boundary Scan Description Language) de chaque composant. Ce fichier, fourni par le fabricant, décrit précisément l’implémentation JTAG du composant et permet à XJTAG d’en tirer parti.

Le test JTAG : pas seulement en production

Contrairement aux tests traditionnels (lits à clous, inspection optique ou rayons X), qui nécessitent des équipements coûteux, le test JTAG peut être réalisé dès le prototypage, avec un simple contrôleur JTAG comme le XJLink2, de la taille d’une souris.

Cela permet aux ingénieurs de :

Cela permet aux ingénieurs de :

- Vérifier les cartes avant même la finalisation du firmware

- Identifier rapidement les défauts de fabrication

- Réutiliser les mêmes tests en production

8 bonnes raisons d’adopter XJTAG pour vos tests

1. BGA : les composants les plus complexes à tester

Les boîtiers à billes (BGA) rendent impossible l’accès physique aux broches. Le boundary scan offre une alternative simple et non intrusive.

2. Éliminer les coûts NRE des bancs de test

Les bancs traditionnels sont coûteux à concevoir. JTAG réduit voire supprime ces besoins.

3. Réduire le temps de test

Par rapport au flying probe, souvent lent, JTAG propose un cycle de test rapide sans équipement lourd.

4. Moins de développement spécifique

Grâce à l’interface normalisée TAP, les tests peuvent être réutilisés d’un projet à l’autre.

5. Un seul outil pour test et programmation

JTAG est déjà utilisé pour la programmation ; autant l’exploiter aussi pour le test.

6. Tester les prototypes comme en production

XJTAG met la puissance des tests industriels à portée des bancs d’ingénierie.

7. Des diagnostics précis pour une réparation rapide

XJTAG localise précisément les défauts, aussi bien sur le schéma que sur le layout.

8. Diagnostiquer des cartes ‘mortes’

Même si une carte ne boote pas, JTAG peut révéler des pannes sur RAM, oscillateurs ou autres périphériques critiques.

Les boîtiers à billes (BGA) rendent impossible l’accès physique aux broches. Le boundary scan offre une alternative simple et non intrusive.

2. Éliminer les coûts NRE des bancs de test

Les bancs traditionnels sont coûteux à concevoir. JTAG réduit voire supprime ces besoins.

3. Réduire le temps de test

Par rapport au flying probe, souvent lent, JTAG propose un cycle de test rapide sans équipement lourd.

4. Moins de développement spécifique

Grâce à l’interface normalisée TAP, les tests peuvent être réutilisés d’un projet à l’autre.

5. Un seul outil pour test et programmation

JTAG est déjà utilisé pour la programmation ; autant l’exploiter aussi pour le test.

6. Tester les prototypes comme en production

XJTAG met la puissance des tests industriels à portée des bancs d’ingénierie.

7. Des diagnostics précis pour une réparation rapide

XJTAG localise précisément les défauts, aussi bien sur le schéma que sur le layout.

8. Diagnostiquer des cartes ‘mortes’

Même si une carte ne boote pas, JTAG peut révéler des pannes sur RAM, oscillateurs ou autres périphériques critiques.

Envie d’aller plus loin ?

Plusieurs options s’offrent à vous :

- Atelier interactif à distance : connectez-vous à un banc d’essai pour découvrir XJTAG en direct avec un expert.

- Essai gratuit de 30 jours : testez le logiciel et le contrôleur XJTAG sur vos propres cartes.

- 15 minutes de conseil personnalisé : échangez avec un expert pour définir la meilleure approche pour votre projet.

Ce guide vous propose un éclairage technique sur la technologie qui sous-tend les solutions XJTAG. Pas d’inquiétude cependant : il n’est pas nécessaire de maîtriser les détails du protocole JTAG pour utiliser les produits XJTAG. Leur fonctionnement s’appuie sur un niveau d’abstraction supérieur, pensé pour l’ingénieur électronique en phase de test et de validation.