# Implementing IEC 61508:2010 with the LDRA tool suite®

# Working with the programmable electronic components sector to achieve functional safety

www.ldra.com

© LDRA Ltd. This document is property of LDRA Ltd. Its contents cannot be reproduced, disclosed or utilised without company approval.

# LDRA

#### Contents

| Introduction                                                                                  | 3  |

|-----------------------------------------------------------------------------------------------|----|

| Safety Integrity Levels                                                                       |    |

| The software development lifecycle                                                            | 4  |

| IEC 61508:2010-3 Section 7.2: "Software safety requirements specification"                    | 5  |

| Bi-directional traceability                                                                   | 6  |

| Static analysis and bi-directional traceability                                               | 7  |

| IEC 61508:2010-3 Section 7.3: "Validation plan for software aspects of system safety"         | 8  |

| IEC 61508:2010-3 Section 7.4.3: "Requirements for software architecture design"               | 8  |

| IEC 61508:2010-3 Section 7.4.4: "Requirements for support tools, including programming        |    |

| languages"                                                                                    | 10 |

| IEC 61508:2010-3 Section 7.4.5: "Requirements for detailed design and development –           |    |

| software system design"                                                                       | 11 |

| IEC 61508:2010-3 Section 7.4.6: "Requirements for code implementation"                        | 12 |

| IEC 61508:2010-3 Section 7.4.7: "Requirements for software module testing" and Section 7.4.8: |    |

| "Requirements for software integration testing"                                               | 12 |

| IEC 61508:2010-3 Section 7.5: "Programmable electronics integration (hardware and software)"  | 14 |

| IEC 61508:2010-3 Section 7.4.6: "Requirements for code implementation"                        | 16 |

| IEC 61508:2010-3 Section 7.7: "Software aspects of system safety validation"                  | 16 |

| IEC 61508:2010-3 Section 7.8: "Software modification"                                         | 16 |

| The connected system – a new significance for system modification                             | 17 |

| IEC 61508:2010-3 Section 7.9: "Software verification"                                         | 19 |

| Conclusions                                                                                   | 20 |

| Works Cited                                                                                   | 21 |

| Appendix: The Annex B tables                                                                  | 22 |

| IEC 61508:2010-3 Annex B Table B.1: "Design and coding standards"                             | 22 |

| IEC 61508:2010-3 Annex B Table B.2: "Dynamic analysis and testing"                            | 22 |

| IEC 61508:2010-3 Annex B Table B.3: "Functional and Black-box testing"                        | 24 |

| Software test and model based development                                                     | 24 |

| IEC 61508:2010-3 Annex B Table B.4: "Failure analysis"                                        | 25 |

| IEC 61508:2010-3 Annex B Table B.5: " <i>Modelling</i> "                                      | 25 |

| IEC 61508:2010-3 Annex B Table B.6: "Performance testing"                                     |    |

| IEC 61508:2010-3 Annex B Table B.7: "Semi-formal methods"                                     | 26 |

| IEC 61508:2010-3 Annex B Table B.8: " <i>Static analysis</i> "                                | 27 |

| IEC 61508:2010-3 Annex B Table B.9: "Modular approach"                                        | 27 |

# LDRA

#### Introduction

With recent advances in automation, software is no longer a bit-part contributor to electro-mechanical systems but is now the underlying technology providing functional safety for products in many market segments. The requirement for software functional safety has therefore become a critical topic in industrial automation, transportation, nuclear energy generation and other markets. IEC 61508:2010 *"Functional safety of electrical/electronic/programmable electronic safety-related systems"* is widely accepted as a reference standard. It also forms the basis for sector-specific standards.

The IEC 61508 standard describes a risk-based approach for determining the SIL (Safety Integrity Level) of safety instrumented functions. If computer system technology is to be effectively and safely exploited, it is essential that the available guidance on these safety related aspects is adequate to allow the correct decisions to be made.

It is recognised that there is a great variety of applications using Electrical/Electronic/Programmable Electronic (E/E/PE) safety-related systems in a range of application sectors, covering a wide range of complexity, hazard and risk potentials. The required safety measures for each particular application will be dependent on many factors specific to it. The generic nature of IEC 61508 makes it an ideal "blank canvas" for the seamless integration of these application dependent factors and hence the derivation of industry and sector specific standards.

In many situations, safety is achieved by a number of systems which rely on many engineering disciplines, including mechanical, hydraulic, pneumatic, electrical, electronic, and programmable electronic technologies. Any safety strategy must therefore consider not only all the elements within an individual system (for example sensors, controlling devices and actuators) but also all the safety-related subsystems which contribute to the safety-related system as a whole. Therefore, although IEC 61508 is concerned with E/E/PE safety-related systems, it also serves as a framework within which safety-related systems based on other technologies may additionally be considered.

This white paper describes the key software development and verification process requirements of the IEC 61508 standard and how automated tools such as the LDRA tool suite<sup>®</sup> and its component parts can assist with meeting them. In general, it is laid out to reflect the flow of the V-model referenced by the standard, but IEC 61508 uses sets of annexed tables to identify particular techniques to be applied. These techniques often apply to different stages of the lifecycle, which makes them difficult to integrate into the narrative illustrated by the "V" model especially when they are sub-referenced. For that reason, descriptions of the annex B tables are held in an appendix.

#### **Safety Integrity Levels**

Embedded software developers will be primarily concerned with part 3 of IEC 61508:2010<sup>1</sup>, "*Software Requirements*". However, the level of effort required to complete each objective in the standard is dependent on the Safety Integrity Level (or "*SIL*") of the safety functions implemented by the system. The derivation of the SIL is covered in more detail in part 5<sup>2</sup> of the standard, "*Examples of methods for the determination of safety integrity levels*".

Annex A of that standard discusses the concept of "*Necessary risk reduction*"<sup>3</sup> and describes it as being "*the reduction in risk that has to be achieved to meet the tolerable risk for a specific situation*". Tolerable risk is dependent on such as the severity of injury, the number of people exposed to danger, and the frequency and duration of that exposure. It is derived by taking due consideration of inputs such as legal requirements, safety authority guidelines, and discussions with interested parties.

The standard goes on to define Safety Integrity as "... the probability of a safety-related system satisfactorily performing the required safety functions under all the stated conditions within a stated period of time"<sup>4</sup> and subdivides it into "Hardware Safety Integrity" and "Systematic Safety Integrity". The latter is the primary concern for software applications.

- systems Part 5: Examples of methods for the determination of safety integrity levels

- <sup>3</sup> IEC 61508:2010-5, Annex A, Section A.2, "Necessary risk reduction"

<sup>&</sup>lt;sup>1</sup> IEC 61508:2010-3, Functional safety of electrical/electronic/programmable electronic safety-related systems – Part 3: Software Requirements <sup>2</sup> IEC 61508:2010-5, Functional safety of electrical/electronic/programmable electronic safety-related

<sup>&</sup>lt;sup>4</sup> IEC 61508:2010-5, Annex A, Section A.4 - Safety Integrity

The SIL assigned to each safety function therefore depends the probability of failure, which can be derived in several different ways. The higher the probability of failure, the higher the SIL (from SIL 1 to SIL 4), and the more demanding the overheads on software development to make the risk acceptable.

| SIL | Low demand mode:<br>average probability of failure on demand | Nigh demend or contiuous mode:<br>probability of dangerous failure per hour       |

|-----|--------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1   | ≥ 10 <sup>-2</sup> t0 < 10 <sup>-1</sup>                     | $\geq$ 10 <sup>-6</sup> to < 10 <sup>-5</sup>                                     |

| 2   | ≥ 10 <sup>-3</sup> to < 10 <sup>-2</sup>                     | ≥ 10 <sup>-7</sup> to < 10 <sup>-6</sup>                                          |

| 3   | ≥ 10 <sup>-4</sup> to < 10 <sup>-3</sup>                     | $\ge$ 10 <sup>-8</sup> to < 10 <sup>-7</sup> ( 1 dangerous failure in 1140 years) |

| 4   | ≥ 10 <sup>-5</sup> to < 10 <sup>-4</sup>                     | ≥ 10 <sup>-9</sup> to < 10 <sup>-8</sup>                                          |

Figure 1: Deriving the SIL of a safety function from the probability of failure

#### The Software Development Lifecycle

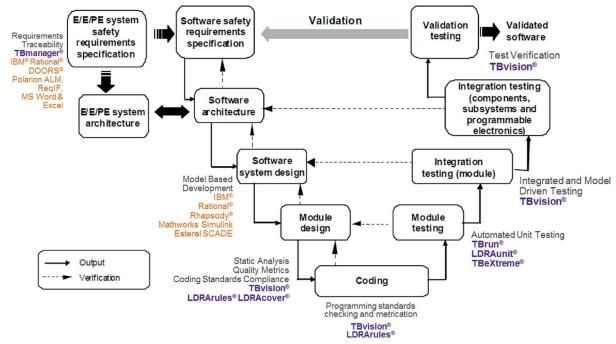

According to the introduction, IEC 61508 "... sets out a generic approach for all safety lifecycle activities for systems comprised of electrical and/or electronic and/or programmable electronic (E/E/PE) elements that are used to perform safety functions." Figure 2 shows the V-model illustration from the standard, superimposed with an illustration of how the LDRA tool suite and other complementary tools can be applied within the process.

Figure 2: Mapping the capabilities of the LDRA tool suite and complementary tools to the IEC 61508:2010 development lifecycle (the V-model)<sup>5</sup>

IEC 61508 is not only a stand-alone standard. It also forms the basis for complete, industry-specific derivative standards such as ISO 26262<sup>6</sup> for the automotive industry, and is also frequently referenced piecemeal when its generic objectives are applicable to more narrowly defined sectors. One such example is the IEC 13849:2015 for control system software, which defers to the development cycle of IEC 61508 for the most critical applications it describes.

Part 3 of IEC 61508, "*Software Safety Lifecycle Requirements*", structures the development of the software in defined phases and activities to reflect and subdivide the phases illustrated in this V-model diagram. These are used as the basis for the layout of this white paper, and comprise:

<sup>&</sup>lt;sup>5</sup> Based on IEC 61508:2010-3 Figure 6 – Software systematic capability and the development lifecycle (the V-model)

<sup>&</sup>lt;sup>6</sup> ISO 26262:2011, Road vehicles – Functional safety

Section 7.2 Software safety requirements specification Section 7.3 Validation plan for software aspects of system safety Section 7.4 Software design and development Section 7.4.3 Requirements for software architecture design Section 7.4.4 Requirements for support tools, including programming languages Section 7.4.5 Requirements for detailed design and development – software system design Section 7.4.6 Requirements for code implementation Section 7.4.7 Requirements for software module testing Section 7.4.8 Requirements for software integration testing Section 7.5 Programmable electronics integration (hardware and software) Section 7.6 Software operation and modification procedures Section 7.7 Software aspects of system safety validation Section 7.8 Software modification Section 7.9 Software verification Section 8 Functional safety assessment

There are also 7 Annexes defined in IEC 61508:2010-3 which are referenced by the main body of the standard. Annex A is discussed in the body of this white paper, and Annex B is considered in an appendix.

#### IEC 61508:2010-3 Section 7.2: "Software safety requirements specification"

The first phase illustrated in the IEC 61508:2010 V-model concerns the definition of a software safety requirements specification. Section 7.2 highlights the objectives associated with the specification of software safety requirements. These include the derivation of requirements for the software safety functions, the software systematic capability, and the implementation of the required safety functions.

The V-model illustrates the need for each step in the process to be traceable to the next, as implied by the verification arrows during the lifecycle, and the validation step at its end. Bi-directional traceability is specified as an explicit objective in the Annex A.1 table (Figure 3) which is typical of the tables used extensively in the standard.

Achieving a format that lends itself to bi-directional traceability will help to achieve compliance with the standard. Bigger projects, perhaps with contributors in geographically diverse locations, are likely to benefit from an application lifecycle management tool such as IBM® Rational® DOORS®7, Siemens® Polarion® PLM®8, or more generally, similar tools offering support for standard Requirements Interchange Formats<sup>9</sup>. Smaller projects can cope admirably with carefully worded Microsoft® Word® or Microsoft® Excel® documents, written to facilitate links up and down the development process model.

|            | Technique/Measure                                                                                  | Ref             |   | S | iL |    |  |

|------------|----------------------------------------------------------------------------------------------------|-----------------|---|---|----|----|--|

|            | ieciniique/measure                                                                                 | Kei             | 1 | 2 | 3  | 4  |  |

| 1a         | Semi-formal methods                                                                                | Table B.7       | R | R | HR | HR |  |

| 1b         | Formal methods                                                                                     | B.2.2,<br>C.2.4 |   | R | R  | HR |  |

| 2          | Forward traceability between the system safety requirements and the software safety requirements   | C.2.11          | R | R | HR | HR |  |

| 3          | Backward traceability between the safety requirements and the<br>perceived safety needs            | C.2.11          | R | R | HR | HR |  |

| 4          | Computer-aided specification tools to support appropriate techniques/measures above                | B.2.4           | R | R | HR | HR |  |

| <b>"R"</b> | "HR" The method is highly recommended for this SIL.<br>"R" The method is recommended for this SIL. |                 |   |   |    |    |  |

| ""         | The method has no recommendation for or against its usage for thi                                  | s SIL.          |   |   |    |    |  |

Figure 3: Copy of IEC 61508-3 Table A.1<sup>10</sup>, with static analysis techniques supported by the LDRA static analysis tools highlighted. Note the specific requirement for bi-directional traceability.

<sup>7</sup> http://www-o3.ibm.com/software/products/en/ratidoor

<sup>&</sup>lt;sup>8</sup> <u>https://polarion.plm.automation.siemens.com/</u>

<sup>9</sup> http://www.omg.org/spec/ReqIF/

<sup>&</sup>lt;sup>10</sup> IEC 61508-3 Annex A Table A.1 – Software safety requirements specification

#### **Bi-Directional Traceability**

It would be easy to dismiss the task of tracing between the development lifecycle phases as trivial, but their combined effect on project management overhead can be significant.

For instance, consider an unexpected change of requirement imposed by a customer. What is impacted? Which requirements? What elements of the code design? What code needs to be revised? And which parts of the software will require re-testing?

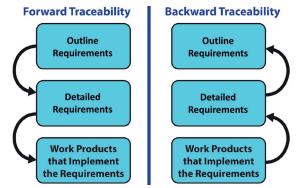

The most effective way to ensure that the project is not thrown off course by such eventualities is to maintain Bi-directional Traceability of Requirements<sup>11</sup> Figure 4). In this diagram, when requirements are managed well, traceability can be established forwards from the outline requirements, through the detailed requirements and on to the work products – and they can similarly be traced backwards. Such bi-directional traceability helps determine that all source requirements have been completely addressed and that all lower level requirements can be traced to a valid source, and that there is no spurious source code that is surplus to requirements. Requirements traceability can also cover the relationships to other entities such as intermediate and final work products, changes in design documentation, and test plans.

Figure 4: An Illustration of the principles of Bi-directional Traceability

Requirements rarely remain unchanged throughout the lifetime of a project, and that can turn the maintenance of a traceability matrix into an administrative nightmare. Furthermore, connected systems extend that scenario into the maintenance phase, requiring revision whenever a vulnerability is exposed.

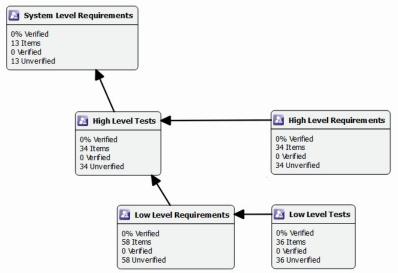

Automating the tracing of requirements alleviates this concern by automatically maintaining the connections between the requirements, development, and testing artefacts and activities. Any changes in the associated documents or software code are automatically highlighted such that any consequential re-testing can be dealt with accordingly (Figure 5).

Figure 5: The Uniview graphic from the TBmanager<sup>®</sup> component of the LDRA tool suite, showing how the relationships between tests and requirements can be configured

6

<sup>11</sup> <u>http://www.westfallteam.com/Papers/Bidirectional\_Requirements\_Traceability.pdf</u> Bidirectional Requirements Traceability, Linda Westfall

#### Static analysis and bi-directional traceability

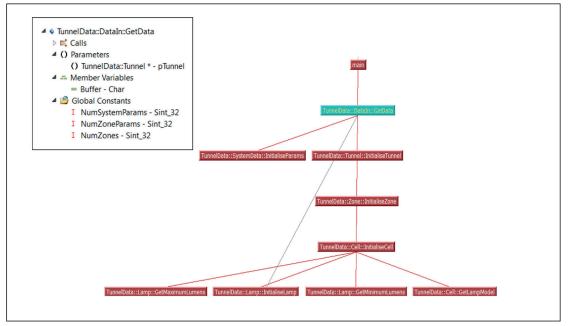

In general, static analysis tools provide a source of evidence that the standard's objectives have been met in the implemented code, and that the designers' vision in meeting those objectives has been realized. For example, IEC 61508:2010-7<sup>12</sup> Sections B.2 and C.2, "*Requirements and detailed design*" require the use of data flow diagrams and decision/truth tables to represent the system design. These lend themselves to verification by means of static analysis later in the lifecycle by means of "*as implemented*" data flow diagrams (Figure 6), LCSAJ (Linear Code Sequence and Jumps) truth tables, and MC/DC (Modified Condition/Decision Coverage) test case analyses.

Figure 6: Diagrammatic representations of control and data flow, generated from source code by the LDRA tool suite, aid verification that software architectural design has been implemented correctly

The reports generated as products of these and other static analysis techniques can be linked to a requirements traceability tool to automate bi-directional end-to-end traceability to and from the system safety requirements and the software safety requirements. Figure 7 shows a fuller list of example IEC 61508 design objectives that can be confirmed to be correctly implemented in the application code using static analysis.

#### IEC 61508:2010-3 Section 7.3: "Validation plan for software aspects of system safety"

This section of the standard is focused on the planning of when, where, how and by whom safetyrelated verification and validation activities are to be carried out. It requires consideration of whether these activities are to be manually or automatically implemented, but the more detailed definition of requirements for the tools themselves are not considered until later in the lifecycle.

#### IEC 61508:2010-3 Section 7.4.3: "Requirements for software architecture design"

Table A.2 in the standard is focused on this "*Requirements for software architecture design*" section. IEC 61508:2010-7 Sections B.2 "*E/E/PE system design requirements specification*", C.2 "*Requirements and detailed design*", and C.3 "*Architecture design*" specify where fault detection techniques need to be implemented as part of the software architecture, such as fault detection, error detection and failure assertion programming. These techniques are designed to highlight failures, thus providing the basis for counter-measures in order to minimize their consequences.

<sup>&</sup>lt;sup>12</sup> IEC 61508:2010-7, Functional safety of electrical/electronic/programmable electronic safety-related systems – Part 7: Overview of techniques and measures

Static analysis techniques can be used to confirm that these sound design objectives are reflected in the code. Examples include Structured Programming Verification (used to identify unstructured code which may lead to erroneous behaviour of the application) and the generation of complexity metrics such as Cyclomatic Complexity and Halstead's metrics (used to help determine the software module size, software complexity and the data flow information). This confirmation of implemented objectives also reflects the need for bi-directional traceability as highlighted in IEC 61508:2010-7 Section C.2.11 *"Traceability"*.

| IEC 61508 reference                                                                                                                          | Assistance from LDRA tools                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEC 61508-3 "Table A.2 – Software design and<br>development – software architecture design - Fault<br>detection" and "Error detecting codes" | Static and dynamic analysis can be used to confirm validity of code implementing these design features                                                                                                                                                                                                                               |

| IEC 61508-3 "Table A.2 – Failure assertion programming"                                                                                      | Can be confirmed using unit and module testing, particularly negative testing                                                                                                                                                                                                                                                        |

| IEC 61508-3 "Table A.2 – Modular approach"                                                                                                   | Can be confirmed by means of structural analysis and its associated reports and charts                                                                                                                                                                                                                                               |

| IEC 61508-3 "Table A.2 – Forward traceability<br>between the software safety requirements<br>specification and software architecture"        | Requirements traceability tool to manage links<br>between requirements, objectives, personnel,                                                                                                                                                                                                                                       |

| IEC 61508-3 "Table A.2 – Backward traceability<br>between the software safety requirements<br>specification and software architecture"       | source code and the other LDRA tools to maintain traceability information in real time                                                                                                                                                                                                                                               |

| IEC 61508-3 "Table A.2 – Structured diagrammatic methods"                                                                                    | Pertinent static analysis techniques including structured programming verification                                                                                                                                                                                                                                                   |

| IEC 61508-3 "Table A.2 – Semi-formal methods"                                                                                                | Formal methods transfer the principles of                                                                                                                                                                                                                                                                                            |

| IEC 61508-3 "Table A.2 – Formal design and refinement methods"                                                                               | mathematical reasoning to the specification and<br>implementation of technical systems. In practical<br>terms, LDRA tools use static analysis of the<br>source code with respect to various programming<br>models (E.g. MISRA C), whilst the parser engine<br>mathematically analyses the structure and<br>provides analysis reports |

| IEC 61508-3 "Table A.3 – Strongly typed<br>programming language" and "Table A.3 –<br>Language subset"                                        | LDRA tools provide code standards checking,<br>including MISRA rules                                                                                                                                                                                                                                                                 |

Figure 7: Examples of IEC 61508 design objectives that can be confirmed as implemented in the application code through the application of LDRA tools

# IEC 61508:2010-3 Section 7.4.4: "*Requirements for support tools, including programming languages*"

This section discusses the selection of the programming language(s) to be used and the associated tool chain for the development of that code, including verification and validation tools (section 7.4.4.2), static code analysers, test coverage monitors and configuration management tools.

IEC 61508:2010-7 Section C.4.5 "Suitable programming languages" recommends that "The programming language chosen should lead to an easily verifiable code with a minimum of effort and facilitate program development, verification and maintenance."

Features which make verification difficult and therefore should be avoided are:

- Unconditional jumps excluding subroutine calls

- Recursion

- Pointers, heaps or any type of dynamic variables or objects

- Interrupt handling at source code level

- Multiple entries or exits of loops, blocks or subprograms

- Implicit variable initialisation or declaration

- Variant records and equivalence and

- Procedural parameters

Static analysis techniques provide automated facilities to check compliance with the programming standards such as MISRA and CERT C which are designed to prevent the introduction of vulnerabilities or latent errors in source code. Such coding standards usually explicitly disallow the use of the programming features identified above, and adherence to these coding standards can be checked automatically (Figure 8).

#### Coding standards

There are many coding standards each with differing attributes but nevertheless with strong similarities, especially when referencing the same language. The most popular standards include:

#### С

MISRA C:1998 MISRA C:2004 MISRA C:2012/AMD1/ADD2 SEI CERT C CWE

#### C++

MISRA C++:2008 JSF++ AV HIC++ SEI CERT C++

**Java** CWE CERT J

| × 💊 | Tuni | nelData::Cell::Cell                                                         |            |                      |                            |

|-----|------|-----------------------------------------------------------------------------|------------|----------------------|----------------------------|

| ~   | **   | Float/integer conversion without cast.                                      | Required   | 435 S                | MISRA-C++:2008 5-0-5       |

|     |      | Float/integer conversion without cast. : (double and int): f                | Required   | 435 S                | MISRA-C++:2008 5-0-5       |

|     |      | Float/integer conversion without cast. : (double and int): f < NumLampTypes | Required   | 435 S                | MISRA-C++:2008 5-0-5       |

|     | ٠    | Pointer subtraction not addressing one array.                               | Required   | 438 S                | MISRA-C++:2008 5-0-17      |

|     |      | Cast to an unrelated type. : (double* to int*): (Sint_32 *) p_f             | Required   | 554 S                | MISRA-C++:2008 3-9-3,5-2-7 |

|     |      | Casting operation on a pointer. : (double* to int*): ( January              |            |                      | MISRA-C++:2008 5-2-7       |

|     |      | Use of C type cast. Standard                                                | s Violatio | MISRA-C++:2008 5-2-4 |                            |

|     | ٠    | Casting operation to a pointer. : (double* to int*): (Sint_32 >> P          | nequireu   |                      | MISRA-C++:2008 5-2-7       |

## Figure 8: Adherence to coding standards guidelines can be checked automatically by LDRA's static analysis tools

Table A.3 from IEC 61508-3 Annex A<sup>13</sup> references the need for "*certified tools and translators*". That implies detailed and thorough testing of those tools, which is a time consuming and costly process.

In most cases, the most cost effective approach is therefore to use a tool that is already approved for the applied standard by an appropriate TÜV certifying organization.

# IEC 61508:2010-3 Section 7.4.5: "*Requirements for detailed design and development – software system design*"

This section of the standard specify design and coding standard enforcement measures pertinent to the source code.

Figure 9 is a reproduction of Table A.4 from Part 3 of the standard, which refers to the sections *"Requirements for detailed design and development"* (7.4.5), *"Requirements for code implementation"* (7.4.6) and C.2 of IEC 61508 (Part 7).

<sup>&</sup>lt;sup>13</sup> IEC 61508:2010-3 Annex A, Table A.3, Software design and development – support tools and programming language

|     | Technicus /Maccust                                                                              | Def                |    | SIL |    |    |

|-----|-------------------------------------------------------------------------------------------------|--------------------|----|-----|----|----|

|     | Technique/Measure*                                                                              | Ref                | 1  | 2   | 3  | 4  |

| 1a  | Structured methods **                                                                           | C.2.1              | HR | HR  | HR | HR |

| 1b  | Semi-formal methods **                                                                          | Table B.7          | R  | HR  | HR | HR |

| 1C  | Formal design and refinement methods **                                                         | B.2.2,<br>C.2.4    |    | R   | R  | HR |

| 2   | Computer-aided design tools                                                                     | B.3.5              | R  | R   | HR | HR |

| 3   | Defensive programming                                                                           | C.2.5              |    | R   | HR | HR |

| 4   | Modular approach                                                                                | Table B.9          | HR | HR  | HR | HR |

| 5   | Design and coding standards                                                                     | C.2.6<br>Table B.1 | R  | HR  | HR | HR |

| 6   | Structured programming                                                                          | C.2.7              | HR | HR  | HR | HR |

| 7   | Use of trusted/verified software elements<br>(if available)                                     | C.2.10             | R  | HR  | HR | HR |

| 8   | Forward traceability between the software safety requirements specification and software design | C.2.11             | R  | R   | HR | HR |

| "HR | "The method is highly recommended for this S                                                    | IL.                |    |     |    |    |

**"R"** The method is recommended for this SIL.

"---" The method has no recommendation for or against its usage for this SIL.

\*\* Group 1, "Structured methods". Use measure 1a only if 1b is not suited to the domain for SIL 3R4.

Figure 9: Copy of IEC 61508-3 Table A.4<sup>14</sup>, with techniques supported by the LDRA static analysis tools highlighted

The software safety requirements require consideration of the following during the design and development phase:

- Completeness with respect to software safety requirements specification

- Correctness with respect to software safety requirements specification

- Freedom from intrinsic design faults

- Simplicity and understandability

- Predictability of behaviour

- Verifiable and testable design

- Fault tolerance / fault detection

- Freedom from common cause failure

The "*Completeness*" and "*Correctness*" are both reflections of the overriding requirement for bidirectional traceability, and that is most easily managed through the application of a requirements traceability tool. The complexity of application code design can be controlled using static analysis to generate industry standard metrics, and industrial coding standards including MISRA C:2012<sup>15</sup>, MISRA C++:2008<sup>16</sup>, SEI CERT C<sup>17</sup>, and JSF++ HR AV<sup>18</sup> are designed to limit the use of constructs most likely to introduce such as common cause failure and unpredictability.

#### IEC 61508:2010-3 Section 7.4.6: "Requirements for code implementation"

This is a short section, mostly consisting of an emphasis for the need for traceability. Best practise dictates that static and dynamic analysis of the code is an ongoing process while the code is being developed, and so the code implementation process is interwoven with module and integration testing, as well as ongoing static analysis.

<sup>17</sup> SEI CERT C Coding Standard, <u>https://wiki.sei.cmu.edu/confluence/display/c/SEI+CERT+C+Coding+Standard</u>

$<sup>^{\</sup>rm 14}$  IEC 61508-3 Annex A Table A.4 – Software design and development – Detailed design

<sup>&</sup>lt;sup>15</sup> MISRA C:2012: Guidelines for use of the C language in critical systems, ISBN 978-906400-11-8 (PDF), March 2013

<sup>&</sup>lt;sup>16</sup> MISRA C++:2008 - Guidelines for the use of the C++ language in critical systems, ISBN 978-906400-04-0 (PDF), June 2008.

<sup>&</sup>lt;sup>18</sup> JSF++ HR AV, JOINT STRIKE FIGHTER AIR VEHICLE C++ CODING STANDARDS FOR THE SYSTEM DEVELOPMENT AND DEMONSTRATION PROGRAM, Document Number 2RDU00001 Rev C, 2005

# IEC 61508:2010-3 Section 7.4.7: "Requirements for software module testing" and Section 7.4.8: "Requirements for software integration testing"

|                                                     | T                                                                                                                          | D-f                         |    | SIL |    |    |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|----|-----|----|----|--|

|                                                     | Technique/Measure                                                                                                          | Ref                         | 1  | 2   | 3  | 4  |  |

| 1                                                   | Probabilistic testing                                                                                                      | C.5.1                       |    | R   | R  | R  |  |

| 2                                                   | Dynamic analysis and testing                                                                                               | B.6.5<br>Table B.2          | R  | HR  | HR | HR |  |

| 3                                                   | Data recording and analysis                                                                                                | C.5.2                       | HR | HR  | HR | HR |  |

| 4                                                   | Functional and black box testing                                                                                           | B.5.1<br>B.5.2<br>Table B.3 | HR | HR  | HR | HR |  |

| 5                                                   | Performance testing                                                                                                        | Table B.6                   | R  | R   | HR | HR |  |

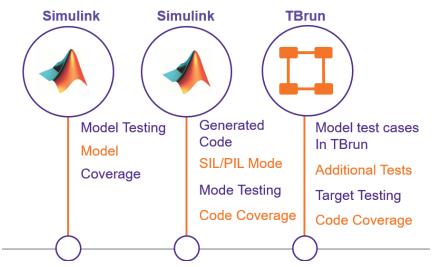

| 6                                                   | Model based testing                                                                                                        | C.5.27                      | R  | R   | HR | HR |  |

| 7                                                   | Interface testing                                                                                                          | C.5.3                       | R  | R   | HR | HR |  |

| 8                                                   | Test management and automation tools                                                                                       | C.4.7                       | R  | HR  | HR | HR |  |

| 9                                                   | Forward traceability between the<br>software design specification and<br>the module and integration test<br>specifications | C.2.11                      | R  | R   | HR | HR |  |

| 10                                                  | Formal verification                                                                                                        | C.5.12                      |    |     | R  | R  |  |

| "HR" The method is highly recommended for this SIL. |                                                                                                                            |                             |    |     |    |    |  |

"R" The method is recommended for this SIL.

"---" The method has no recommendation for or against its usage for this SIL.

*Figure 10: Copy of IEC 61508-3 Table A.5*<sup>19</sup>, with techniques supported by the LDRA static analysis tools highlighted

Figure 10 is a reproduction of IEC 61508-3 Table A.5, which refers to IEC 61508-3 Section 7.4.7 "*Software module testing*", IEC 61508-3 Section 7.4.8 "*Requirements for software integration testing*", and IEC 61508-7 Section C.5 "*Verification and modification*". These sections identify methods designed to contribute to the achievement of software safety, such as software module testing and software integration testing.

A combination of code review and software module testing verifies that a software module satisfies its associated specification. Software module testing in particular lends itself well to several objectives specified in the standard:

- Completeness of testing with respect to the software design specification

- Correctness of testing with respect to the software design specification (successful completion)

- Repeatability

- Precisely defined testing configuration

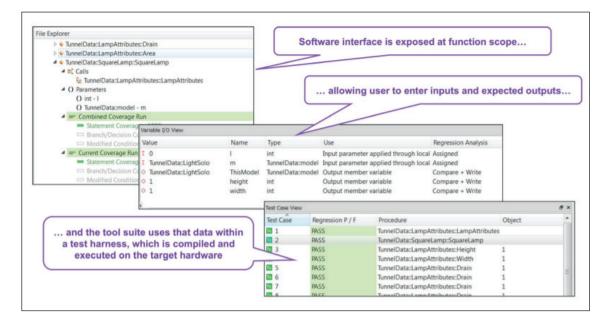

Although module testing can be performed by writing custom code for the purpose, the use of a certified, proven test tool is likely to be much more cost effective unless the code base is very small. Such a tool can automatically generate test drivers and harnesses (wrapper code) with no extra coding or scripting required, enabling tests to be easily and efficiently run on code units (Figure 11).

<sup>&</sup>lt;sup>19</sup> IEC 61508-3 Annex A Table A.5 – Software design and development –Software module testing and integration

Figure 11: Performing requirement based unit-testing using the TBrun® component of the LDRA tool suite

These tests can be subsequently regressed, with clear maintenance tracking and seamless storage of test data and results.

#### IEC 61508:2010-3 Section 7.5: "Programmable electronics integration (hardware and software)"

|            | Technique/Measure                                                                                                                                                              | Ref                         |    | S  | IL |    |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----|----|----|----|--|

|            | lecinique/measure                                                                                                                                                              | Kei                         | 1  | 2  | 3  | 4  |  |

| 1          | Functional and black box testing                                                                                                                                               | B.5.1<br>B.5.2<br>Table B.3 | HR | HR | HR | HR |  |

| 2          | Performance Testing                                                                                                                                                            | Table B.6                   | R  | R  | HR | HR |  |

| 3          | Forward traceability between the system and<br>software design requirements for hardware/<br>software integration and the hardware/software<br>integration test specifications | C.2.11                      | R  | R  | HR | HR |  |

| <b>"R"</b> | "HR" The method is highly recommended for this SIL.                                                                                                                            |                             |    |    |    |    |  |

Figure 12: Copy of IEC 61508-3 Table A.6<sup>20</sup>, with techniques supported by the LDRA static analysis tools highlighted

It is necessary for the integrated software to be proven on the target programmable electronic hardware by means of a number of specified test techniques. Depending on the SIL, these may include:

- Functional Tests

- Black box tests, to check the dynamic behaviour under real functional conditions, which reveal failures to meet the functional specification

- This includes testing data from:

- Permissible ranges

- Inadmissible ranges

- The range limits

- Extreme values

- Combinations of the above classes

<sup>20</sup> IEC 61508-3 Annex A Table A.6 - Programmable electronics integration (hardware and software)

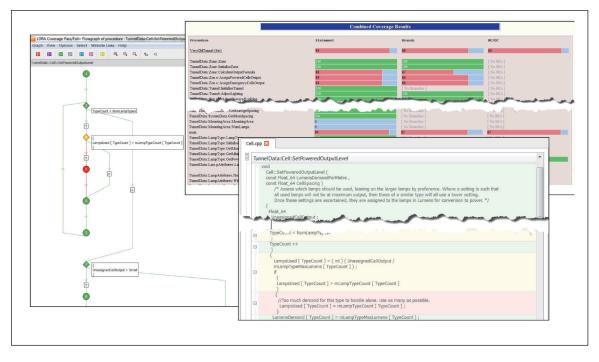

Function and call coverage can be supported by unit test, system test, or a combination of the two operating in tandem (Figure 13). For instance, a preferred approach for a particular project might be to use dynamic system test to generate coverage of most of the source code. That data could then be complemented by coverage generated during unit tests designed to exercise code constructs which are inaccessible during normal operation, such as defensive code.

Figure 13: Examples of representations of structural coverage within the LDRA tool suite

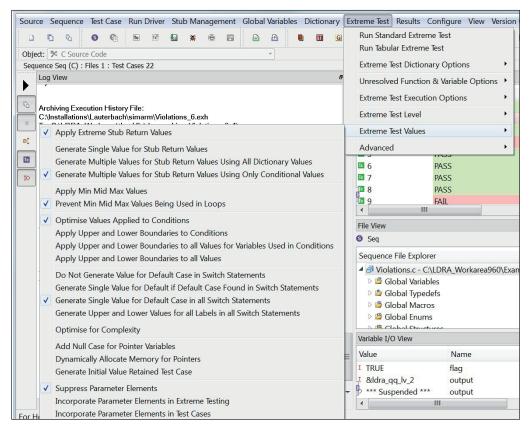

To complement this structural coverage analysis, boundary values could be provided manually or generated automatically (Figure 14) to check the permissible and inadmissible ranges.

Figure 14: Using the TBrun and TBeXtreme<sup>®</sup> components of the LDRA tool suite to automatically create boundary value tests

#### IEC 61508:2010-3 Section 7.4.6: "Requirements for code implementation"

Aside from emphasizing the need for bi-directional traceability, this section is largely a stub, cross-referencing other sections of the standard.

#### IEC 61508:2010-3 Section 7.7: "Software aspects of system safety validation"

Figure 15 is a reproduction of IEC 61508-3 Table A.7 from the standard, which refers to IEC 61508-3 Section 7.7 "Software aspects of system safety validation" and IEC 61508-7 Section C.2 "Requirements and detailed design". These sections specify the software aspects of system safety validation. These ensure that the integrated system complies with the software safety requirements specification at the required safety integrity level.

|                                                                                                                                                                                                                  | Technique/Measure                                                                                                             | Dof                         | Ref |    |    |    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|----|----|----|--|

|                                                                                                                                                                                                                  | Technique/Measure                                                                                                             | Kei                         | 1 2 |    | 3  | 4  |  |

| 1                                                                                                                                                                                                                | Probabilistic testing                                                                                                         | C.5.1                       | ••• | R  | R  | HR |  |

| 2                                                                                                                                                                                                                | Process simulation                                                                                                            | C.5.18                      | R   | R  | HR | HR |  |

| 3                                                                                                                                                                                                                | Modelling                                                                                                                     | Table B.5                   | R   | R  | HR | HR |  |

| 4                                                                                                                                                                                                                | Functional and black-box testing                                                                                              | B.5.1<br>B.5.2<br>Table B.3 | HR  | HR | HR | HR |  |

| 5                                                                                                                                                                                                                | Forward traceability between the<br>software safety requirements<br>specification and the software safety<br>validation plan  | C.2.11                      | R   | R  | HR | HR |  |

| 6                                                                                                                                                                                                                | Backward traceability between the<br>software safety validation plan and<br>the software safety requirements<br>specification | C.2.11                      | R   | R  | HR | HR |  |

| <ul> <li>"HR" The method is highly recommended for this SIL.</li> <li>"R" The method is recommended for this SIL.</li> <li>"" The method has no recommendation for or against its usage for this SIL.</li> </ul> |                                                                                                                               |                             |     |    |    |    |  |

#### *Figure 15: Copy of IEC 61508-3 Table A.7<sup>21</sup>, with techniques supported by the LDRA tool suite highlighted.*

Functional and Black-Box testing can be used to check whether the functions of a system or program behave as the specification dictates when executed in a prescribed environment according to established criteria, and the associated configuration files can be stored and used for the automated regression analysis to confirm ongoing adherence to the specified requirements.

Automated requirements traceability tools complement this by providing forward and backward traceability between the software safety requirements specification and software safety validation plan.

#### IEC 61508:2010-3 Section 7.8: "Software modification"

Figure 16 is a reproduction of IEC 61508-3 Table A.8 from the standard, which refers to IEC 61508-3 Section 7.8 "*Software modification*" and IEC 61508-7 Section C.5 "*Verification and modification*".

These sections specify the steps to be followed during the modification of software. They provide guidance on the implementation of corrections, enhancements and adaptations of validated software, ensuring that the adherence to IEC 61508 for the resulting modified system is not compromised.

<sup>&</sup>lt;sup>21</sup> IEC 61508-3 Annex A Table A.7 – Software aspects of system validation

|              | Taba:                                                                                                                                                                | Def       |     | S  | IL |    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|----|----|----|

|              | Technique/Measure                                                                                                                                                    | Ref       | 1   | 2  | 3  | 4  |

| 1            | Impact analysis                                                                                                                                                      | C.5.23    | HR  | HR | HR | HR |

| 2            | Reverify changed software module                                                                                                                                     | C.5.23    | HR  | HR | HR | HR |

| 3            | Reverify affected software modules                                                                                                                                   | C.5.23    | R   | HR | HR | HR |

| 4a           | Revalidate complete system                                                                                                                                           | Table A.7 | ••• | R  | HR | HR |

| 4b           | Regression validation                                                                                                                                                | C.5.25    | R   | HR | HR | HR |

| 5            | Software configuration management                                                                                                                                    | C.5.24    | HR  | HR | HR | HR |

| 6            | Data recording and analysis                                                                                                                                          | C.5.2     | HR  | HR | HR | HR |

| 7            | Forward traceability between the Software<br>safety requirements specification and<br>the software modification plan (including<br>reverification and revalidation)  | C.2.11    | R   | R  | HR | HR |

| 8            | Backward traceability between the software<br>modification plan (including reverification<br>and revalidation) and the software safety<br>requirements specification | C.2.11    | R   | R  | HR | HR |

| " <b>R</b> " | "HR" The method is highly recommended for this SIL.                                                                                                                  |           |     |    |    |    |

Figure 16: Copy of IEC 61508-3 Table A.8<sup>22</sup> , with techniques and measures supported by the LDRA tool suite highlighted

The following techniques and measures should be considered with regards to software modification:

- Completeness of modification with respect to its requirements

- Correctness of modification with respect to its requirements

- Freedom from introduction of intrinsic design faults

- Avoidance of unwanted behaviour

- Verifiable and testable design

- Regression testing and verification coverage

In this context, impact analysis is designed to determine whether a change or an enhancement to a software system has affected its overall functionality, or has the potential to do so. There are three possible conclusions:

- Only the changed software module needs to be re-verified

- All affected software modules need to be re-verified, or

- The complete system needs to be re-verified

The level of re-verification required will be influenced by the number of software modules affected, the criticality of the affected software modules, and the nature of the change.

#### The connected system – a new significance for system modification

With the advent of the connected device and the Internet of Things, system maintenance takes on a new significance. For any connected systems, requirements don't just change in an orderly manner during development. They change without warning - whenever some smart Alec finds a new vulnerability, develops a new hack, or compromises the system. And they keep on changing throughout the lifetime of the device.

For that reason, the ability of next-generation automated management and requirements traceability tools and techniques to create relationships between requirements, code, static and dynamic analysis results, and unitand system-level tests is especially valuable for connected systems. Linking these elements already enables the entire software development cycle to become traceable, making it easy for teams to identify problems and

<sup>&</sup>lt;sup>22</sup> IEC 61508-3 Annex A Table A.8 – Modification

implement solutions faster and more cost effectively. But they are perhaps even more important after product release, presenting a vital competitive advantage in the ability to respond quickly and effectively whenever security is compromised.

Many software modifications will require changes to the existing software functionality – perhaps with regards to additional utilities in the software. In such circumstances, it is important to ensure that any changes made or additions to the software do not adversely affect the existing code.

A requirements traceability tool can help to alleviate this concern by automatically maintaining the connections between the requirements, development, and testing artefacts and activities. In the example shown in Figure 18, suppose that a change is proposed to the system requirement "*Installation and configuration*". The traceability established at development time between requirements, code and tests mean that the tool can show which parts of the code are impacted by the proposed change, as highlighted in the example.

| System Requirements                                                                                                 | Software High-Leve<br>Requirements                                                                                                               | '                                                              | Softwar<br>Require                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | re Low-Level<br>ements                                                                                                                                                                                                                                                                                                                                                                         | Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| (0) Three-Level Requirements to Mappings 🛛 🚺                                                                        |                                                                                                                                                  |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| <> - Select None * (13) Requirements 1                                                                              | < > - Select None * (34) Requirement                                                                                                             | ts 2                                                           | < > - Select None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>(58) Requirements 3</li> </ul>                                                                                                                                                                                                                                                                                                                                                        | < > - Select None * (47) Mappings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |